A recent paper by EECS Assistant Professor Ahmedullah Aziz’s research group has been named an “Editor’s Pick” by the prestigious journal in which it was published, Applied Physics Letters. Their paper, entitled “A Cryogenic Memory Array Based on Superconducting Memristors,” presents a novel design for a cryogenic memory array utilizing superconducting memristors as memory elements, and heater cryotrons as access controllers. This research was conducted in collaboration with Princeton University.

Memory devices are used to store digital information in a binary format. They are ubiquitous and essential parts of the digital world. We are living in a data-driven civilization where the amount of digital information is growing exponentially. While the need for high-capacity storage solutions can be easily understood, the purpose of “cryogenic memories” may not be immediately clear. “Cryogenic memories are specially designed to operate at or below the liquid Helium temperature (-452 degrees Fahrenheit),” Aziz explained. “For obvious reasons, these memories cannot be used as regular storage in consumer electronic products. These devices are specifically designed for quantum computing systems, space electronics, and high-performance computing with superconducting processors.”

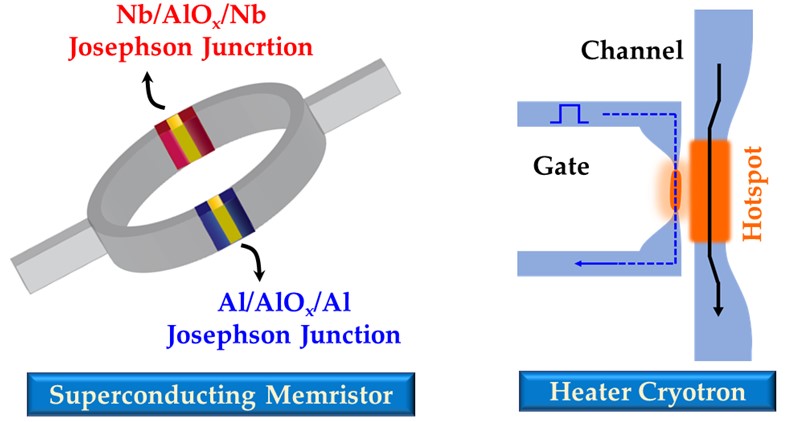

Shamiul Alam, a third-year PhD student advised by Aziz, is the lead author of this article. He briefly described the technical details of the underlying technology, saying “a superconducting memristor comprises two parallel-connected Josephson junctions with identical critical current, but asymmetric conductance levels. This device can be programmed to exhibit two different resistance levels to represent binary digits – 0 and 1. On the other hand, a heater cryotron is made by coupling a superconducting nanowire with a non-superconducting control gate metal. It is possible to switch between superconducting and non-superconducting modes using controlled current-flow through the gate metal. Thus, the heater cryotron can be used as a switch to selectively access the memory elements within the array.”

Their collaborator, Professor Md Shafayat Hossain of Princeton University added, “our proposed array architecture can potentially enable large-scale cryogenic memory array without the need for complex inductive coupling that are customary in most superconducting memory topologies.”

The research group’s paper is available here.

To learn more about Aziz’s group and their ongoing research efforts, please visit NorDIC Lab.